Instruction pipelining is a technique of organising the instructions for execution in such a way that the execution of the current instruction is overlapped by the execution of its subsequent instruction. Instruction pipelining improves the performance of the processor by increasing its throughput i.e. number of instructions per unit time.

In this context, we will discuss the instruction pipelining, how it works along with the pipelining hazards. We will also discuss some advantages of instruction pipelining.

Content: Instruction Pipelining in Computer Architecture

- Instruction Pipelining

- Instruction Pipelining Hazardous

- Advantages of Instruction Pipelining

- Key Takeaways

What is Instruction Pipelining?

Consider that we have a set of instructions to get executed, let us see how it begins? The processor fetches an instruction from the memory, decode the instruction and determine the kind of operation that has to be performed. If the operation requires operands then the processor fetches the operands from the memory and then perform the required operation. Finally, the processor stores the result to the specified memory location.

In this way, the processor processes each instruction from the start till it finishes execution and then it fetches the next instruction for instruction. Now if we divide the instruction execution into stages then it could be divided into:

- Instruction fetches: Fetch the instruction from the main memory or cache.

- Instruction decoding: The processor interprets instruction and determines the operation that has to be performed.

- Operand fetch: If the execution of the instruction requires operand then the processor fetches operand from the main memory or cache.

- Instruction Execution: The processor performs the desired operation.

- Operand Store: The result of execution is stored.

Now each stage is handled by the different sections of the hardware. So, once the instruction is fetched by the fetching unit of the hardware and is forwarded to other hardware section for decoding, operand fetches, execution and operand store; the fetching unit of hardware has to sit idle till the operand store stage is completed.

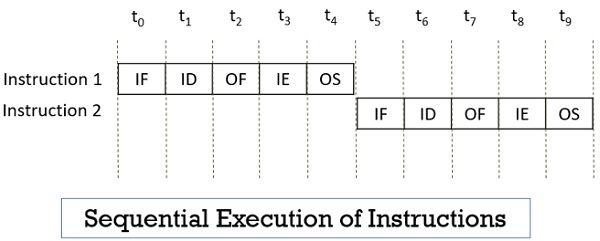

The figure below shows you the sequential execution of the instruction processing one stage in one clock cycle.

This reduces the efficiency of the system. Thus to improve the systems efficiency instruction pipelining can be implemented. Instruction pipelining lets different hardware sections to process different instructions simultaneously.

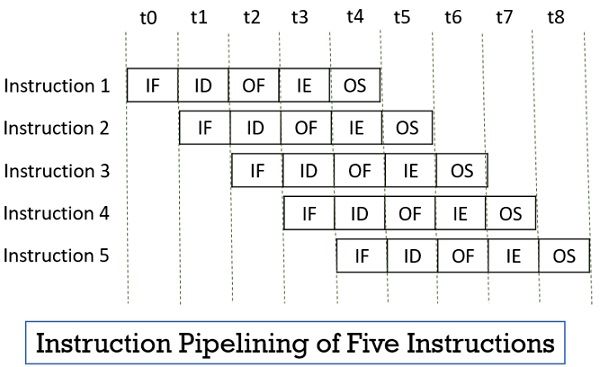

The figure below shows you how the pipelined instruction reduces the processing time of several instructions and improves the efficiency of the system. Notice that the instruction decode stage of instruction 1 is overlapped with the instruction fetch stage of instruction 2.

It is noticeable how the instruction pipelining speed up the processing time of the processor. Like when the instructions are executed sequentially only two instruction are executed in 10 clock cycles where when the instructions are pipelined five instructions are executed in 9 clock cycles.

Instruction Pipelining Hazards

The instruction pipelining hazards is a condition where the execution of the pipelined instructions is stopped or delayed, it is also called a pipeline bubble. There are three kinds of instruction pipeline hazards.

Resource Hazards

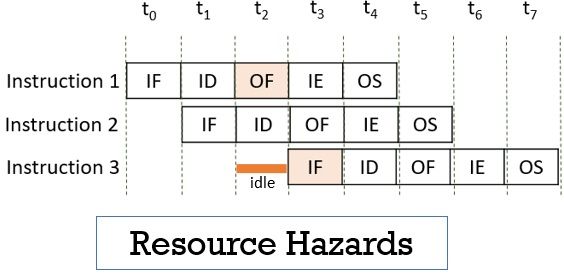

When two pipelined instructions or even more, want to access the same resource it results in resource hazards. It is also termed structural hazards. A solution to this hazard is that these instructions must be executed serially up to some portion of the pipeline.

Let us understand this with the help of an example. Consider the main memory you have has a single port that restricts the processor to perform instruction fetch, read data and write data one at a time. This means you cannot perform the operand read & write operation, from memory in parallel with instruction fetch.

Now consider that there are three instructions in the pipeline. So in the normal conditions, the operand fetch of instruction 1 must-have overlapped the instruction fetch of instruction 3. But there is a case that source operand of instruction 1 is present in main memory instead of register and the rest of all the operands are in register. So we would halt the instruction fetch of instruction 3 for one clock cycle. Because instruction 1 will fetch its source operand from memory so in the same clock cycle instruction 3 cannot perform instruction fetch in parallel to operand fetch of instruction 1.

Data Hazards

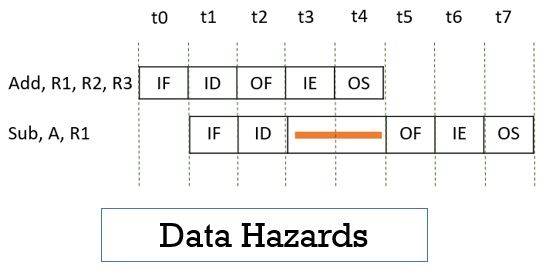

The data hazard is a condition when accessing an operand location creates conflict. Consider that you have two instructions:

ADD R1, R2, R3

SUB A, R1

Observe the instructions above the result of add instruction is stored in register R1 after the execution. This R1 act as an operand for subtract instruction. Now in the figure below notice that the register R1 is updated with the add result in clock cycle t4. But the subtract instruction need its operand R1 at the t3 clock cycle. But if subtract instruction fetches the operand R1 in the t3 clock cycle then it will generate an incorrect result.

So the subtract instruction must stall or halt for two clock cycles because for the correct result the subtract instruction is dependent on the result of add instruction. This dependency is also called data dependency.

Control Hazards

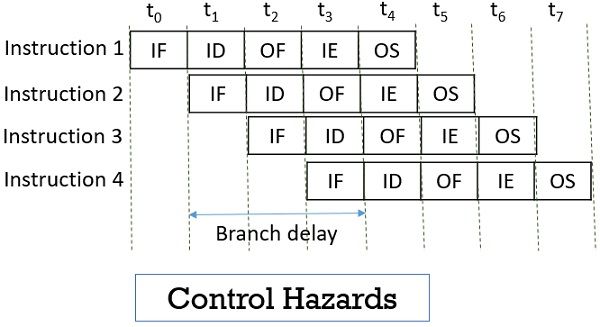

Control hazards occur when instruction pipelining fails in predicting branches in the instruction. Let us understand this with the help of an example. Consider the first instruction I1 in the pipeline is a branch instruction that targets instruction I6.

The instruction I1 is fetched in cycle t0, decoded in cycle t1, fetch operands in cycle t2 and perform execution in cycle t3 where the target address is computed. But till then three instructions I2, I3 and I4 are pipelined in cycle t1, t2 and t3 which must be discarded as instruction I1 is branch instruction which will compel the processor to execute the instruction I9 after instruction I1.

This is how control hazards lead to delay of three cycles t1, t2 and t3 between I1 and I 6 which is also termed as branch delay.

This branch delay could be minimized if the branches in the instruction could be predicted at the decoding stage only.

Advantages of Instruction Pipelining

- Instruction pipelining increases instruction throughput.

- Instruction pipelining let all the stages i.e. instruction fetch, instruction decode, operand fetch, execute and operand store to be performed parallel.

- In every clock cycle, an instruction completes its execution.

Key Takeaways

- Instruction pipelining organizes the instructions to be executed in such a way that the execution of current instruction is overlapped by the execution of the subsequent instruction.

- If the instruction is divided into stages like instruction fetch, instruction decode, operand fetch, execute and operand store then in instruction pipelining all the stages are performed parallel.

- Though instruction pipelining make multiple instructions execute simultaneously but it restricts two or more instruction executing the same stage in the same clock cycle.

- Resource hazards, data hazards, control hazards are the instruction pipeline hazards that occur when the pipelined instruction stall their execution due to some conditions.

Thus instruction pipelining is a method that is used to implement modern microprocessor and microcontroller to increase the throughput of the processor.

Leave a Reply