CISC is an abbreviation for Complex Instruction Set Computer. CISC processors were evolved in the 1970s before the evolution of RISC (Reduced Instruction Set Computers) processors. During this period the computer memory uses to be ‘small’ and ‘very expensive’.

CISC processors were helpful in simplifying the code and making it shorter in order to reduce the memory requirement. In a CISC processor, a single instruction has ‘several low-level operations’. This makes the CISC instructions short but ‘complex’.

In this section, we will learn about the architecture, instruction set, pipelining in CISC processors and its advantages and disadvantages. So let us start with the topic.

Content: CISC Processors

- CISC Architecture

- CISC Instruction Set

- Pipelining in CISC Processor

- Advantages and Disadvantages

- Key Takeaways

CISC Processors Architecture

As we have studied above the main objective of a CISC processor is to minimize the program size by reducing the number of instructions in a program. This is done by ’embedding some of the low-level instructions in a single complex instruction’. Later when decoded this instruction generates several microinstructions to execute.

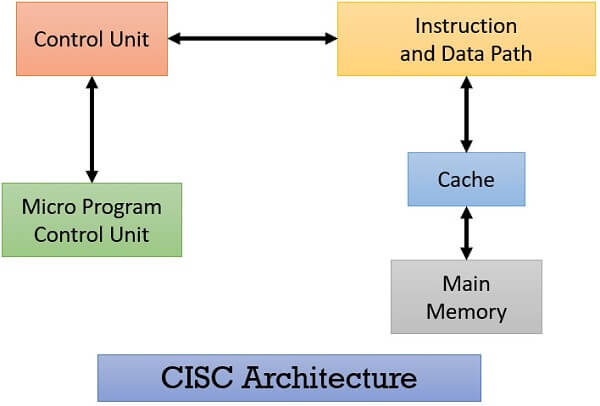

Now if a program/software is getting simplified then the hardware has to get on work and must be able to perform the complex tasks. That’s why a CISC processor has complex hardware. The block diagram of CISC architecture is given below:

Here, you have a special microprogram control unit that uses a series of microinstructions of the microprogram stored in the “control memory” of the microprogram control unit and generate the control signals.

The control units access the control signals produced by the microprogram control unit & operate the functioning of processors hardware.

Instruction and data path fetches the opcode and operands of the instructions from the memory.

Cache and main memory is the location where the program instructions and operands are stored.

Examples of CISC Processors are:

IBM 370/168, VAX 11/780, Intel 80486.

CISC Processors Instruction Sets

CISC instructions are complex in nature and occupy more than a single word in memory. Like RISC uses Load/Store for accessing the memory operands, CISC has Move instruction to access memory operands.

But, unlike Load and Store, the Move operation in CISC has wider scope. The CISC instructions can “directly access memory operands”.

The general format of Move instruction is

Move destination, source

It can move an immediate operand, to a memory location or a register.

Move A, 100

Move R, 100

It can transfer the operand between two memory location.

Move A, B

It can transfer the operand between two registers.

Move R1, R2

Including the five basic addressing mode like:

Immediate mode, direct/absolute mode, register mode, Indirect mode and Index mode.

CISC instruction set has some additional addressing modes. Those are “auto increment mode”, “auto decrement mode” and “relative mode”.

Autoincrement mode:

Here, the effective address of an operand is the content of the register. After accessing the register’s content, it is automatically incremented to point the memory location of next operand.

Auto decrement mode:

Here also, the effective address of an operand is the content of the register. But, here initially, the content of register is decremented and then the content of register is used as an effective address for an operand.

Relative Mode:

It is similar to “Index register mode” where the effective address is obtained by adding a constant to the content of the general-purpose register. In relative mode instead of a general-purpose register, the program counter is used. This kind of addressing mode is used to refer large range of area in memory.

Now above we have mentioned that the CISC processor minimizes the number of instructions which turns the length of code relatively shorter.

Let us see how the CISC style instructions minimizes the code length?

Suppose, we have an operation

A= B+C

RISC instruction set for this would be:

Load R2, B

Load R3, C

Add R4, R2, R3

Store R4, A

Now, let us see the CISC instruction set for the same operation.

Move A, B

Add A, C

The objective of four RISC style instructions is fulfilled by only two instructions of the CISC style.

So we can say that CISC architecture effectively minimizes the number of instructions in the program as a single instruction execution, executes several low-level instructions in a program.

Pipelining in CISC Processors

RISC style instructions provide ease to implement pipelining as they all are of one word. The operands of all the instructions are present in the same position within the word. Excluding Load and Store instructions all other instruction operate on the register operands.

So it becomes easy to implement pipelining for RISC style instructions. But, same is not in the case of CISC style instructions. CISC instructions are of “variable length”, they have “multiple operands”, “complex addressing modes” & “complex instructions”.

Now, CISC instruction occupies more than a memory word. So it will take several cycles for operand fetch. Further, we know instructions are of variable sizes and format, this complicates the decoding of instruction and operand fetch. That’s why implementing pipelining to CISC style instructions is a complicated task.

Let us understand this with the help of an example:

Move (R2), (R3)

Move (R4), R5

In the first Move instruction, the effective address of both the operands is a memory location. So, it will require two memory accesses.

In the second Move instruction, the effective address of the ‘first operand’ is a memory location and effective address of the ‘second operand’ is a register. The second instruction needs only one memory access. Here, the second Move instruction needs to be stalled so, that the first Move instruction can complete accessing of both the operands from the memory.

Hence, implementing pipelining to CISC style instructions is quite complicated.

Advantages and Disadvantages of CISC Processors

Advantages:

- The code size is comparatively shorter which minimizes the memory requirement.

- Execution of a single instruction accomplishes several low-level tasks.

- Complex addressing mode makes the memory access flexible.

- CISC instruction can directly access memory locations.

Disadvantages:

- Though the code size is minimized but it requires several clock cycles to execute a single instruction. Thereby reduce the overall performance of the computer.

- Implementing pipelining for CISC instruction is a bit complicated.

- The hardware structure needs to be more complex to simplify software implementation.

- Designed to minimize the memory requirement when memory was smaller and costlier. But today the scenario has changed nowadays memory is inexpensive and mostly all computers have a large amount of memory.

Key Takeaways

- CISC processor was introduces before the evolution of RISC processor. It was not that the CISC was a wrong approach both CISC and RISC were developed on a different spectrum.

- CISC processor have instructions that occupy more than one memory word.

- A single instruction has several low-level instructions.

- Each instruction requires more than one clock cycle.

- CISC instructions have complex addressing modes, complex instructions; hence decoding of instruction is also complex.

- CISC instructions can directly operate on memory operand.

- The program size is smaller as fewer but complex instructions are used.

So this is all about CISC processors. The recent CISC processor include some of the RISC characteristics.

Sarvesh Gawand says

I need Example .