The structure of the instruction cycle defines the processing of a single instruction. The processing of instruction takes various form during the occurrence of an interrupt or if there is indirect addressing present in the instruction. In this section, we will discuss various forms of the instruction cycle.

Instruction Cycle Definition

The processing involved in the execution of a single instruction is termed as Instruction Cycle. This processing is done in two steps i.e. fetch and execute. To execute an instruction the processor first reads an instruction from the memory which is called fetching and then the fetched instruction is executed.

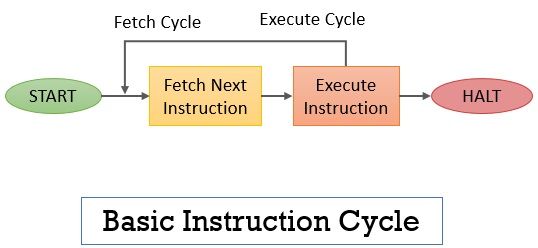

If we discuss the basic structure it includes the following two cycles:

- Fetch cycle: In this cycle, the processor reads the instruction that is to be executed from the memory.

- Execute cycle: In this cycle, the processor interprets the opcode of the fetched instruction and performs the operations accordingly.

The figure below shows you the processing of the basic instruction cycle. In the beginning, to start the execution of a program, the processor runs the fetch cycle and fetches the first instruction from the memory. The execution cycle interprets the operation and performs the operations specified in the instruction accordingly.

This cycle repeats until all the instructions are executed from the program and after the execution of the last instruction the instruction cycle get halt. So, this was the scenario where there were no interrupts.

Interrupt Cycle

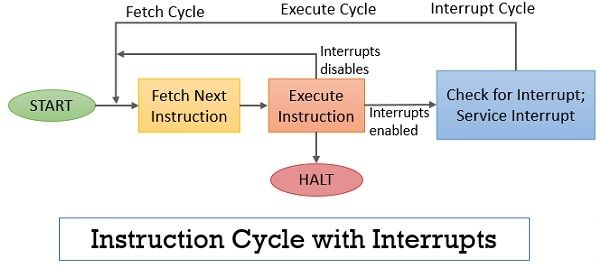

To accommodate the occurrence of interrupts the interrupt cycle must be added to amend the structure of the instruction cycle. As in the figure below you can see the interrupt cycle has been added to the basic instruction cycle.

Consider the condition that the interrupts are enabled. In this case, if an interrupt occurs then the processor halt the execution of the current program. Thereby it saves the address of the instruction that has to be executed next and service the occurred interrupt.

To process the interrupts the processor set the program counter with starting address of the interrupt service routine. This would let the processor fetch the first instruction of interrupt service routine and service the occurred interrupt. Once the interrupt is serviced the processor resumes back to the execution of the program it has halted to service the interrupt. It set the program counter with the address of the next instruction to be executed.

If the interrupts are disabled then the processor will simply ignore the occurrence of interrupts. The processor will smoothly execute the currently running program and will check the pending interrupts once the interrupts are enabled.

Indirect Cycle

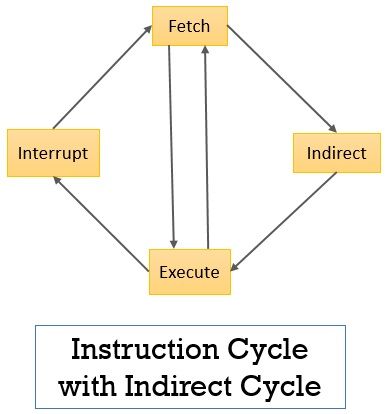

An instruction may have one or more than one operands. To operate these operands its value is accessed from the memory. So, to execute the instructions with operands we require memory access. Now, what if indirect addressing is used?

Additional memory access is required if indirect addressing is used in the instructions. This adds one more stage or cycle to the basic instruction cycle. Basically, the instruction fetch and instruction execute cycle occurs alternatively.

The fetched instruction is checked for indirect addressing. If indirect addressing is present the operands are fetched by performing an indirect cycle. And if there occurs an interrupt it is processed before the execution of the next instruction.

Flowchart

The structure of the instruction cycle varies from processor to processor depending on its design. Though if we talk in general terms let us see what must happen. Before getting into the details let us discuss the registers that are required in the processing of the instruction cycle.

- Memory Address Register (MAR): This register holds the address of memory location from where the data has to be fetched or to where the data has to be stored.

- Memory Buffer Register (MBR): This register stores the data that is either fetched from the memory or that has to be stored in the memory.

- Program Counter (PC): This is also called the instruction address register as it holds the address of the instruction that has to be executed next.

- Instruction Register (IR): This register holds the instruction that has to be interpreted.

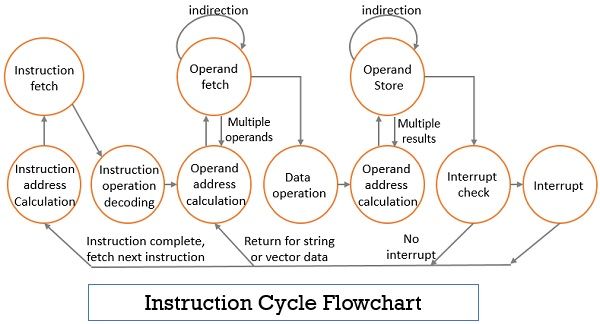

The figure below shows you the flowchart of the instruction cycle with interrupts and indirect addressing.

Initially fetch cycle will run, the program counter is initialized by the address of the first instruction of the program. The address in PC is transferred to the MAR and the PC is updated with the address of the next instruction to be executed. The control unit reads the instruction from the address present in MAR and store it in MBR and then transfers it to IR. Here the fetch cycle gets over.

The control unit checks the IR to verify if the instruction has any operands present, specifying indirect addressing. If the indirect addressing is present in the instruction then the indirect cycle has to be run.

For this, the control unit reads the right-most N bits of MBR and transfer them to the MAR. These N bits contain the address reference of the operand that has to be fetched. The control unit performs the memory read operation and fetch the address of the operand and transfer it into MBR. Here the indirect cycle gets over.

The execution cycle may be of various form and it totally depends on the type of instruction present in the IR. The execute cycle involves transferring data from registers to registers, read memory or write memory operations, ALU operations.

The interrupt cycle starts when there arises an interrupt signal. The PC has the address of the next instruction of the program that has to be executed next. The content of PC i.e. address of the next instruction that has to be executed is transferred to MBR. Now the content of MBR is written to a special memory location the address of which is loaded into MAR. Now the PC is initialized with the first instruction of interrupt service routine, this program’s services the occurred interrupts.

So, these are the various forms of the instruction cycle. We have seen the amendment in its structure when there is indirect addressing present in the instructor and even when an interrupt occurs.

Leave a Reply