Instructions in a program have proper instruction format and sequencing which decides the flow of the program execution. There are several types of instructions in a computer program like:

- instruction performing arithmetic or the logic operation on the numbers

- instruction that branches to other instruction in the program

- the instruction that checks the particular condition and many more

In this section, we will be discussing a different kind of Instructions, their notations, about RISC and CISC instructions, about the sequencing and controlling instructions and branching instructions. So let us start.

Content: Instruction Format and Sequencing

- Instruction Format &Types

- Register Transfer Notation

- Assembly Language Notation

- RISC and CISC Instruction set

- Instruction Sequencing and Execution

- Branching Instruction

Instruction Format & Types

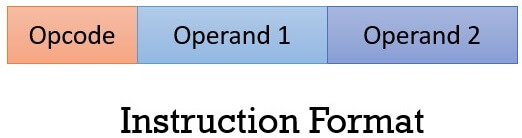

Before studying more about the instruction let us understand the basic format of instruction. Below is the figure showing the general format of the instruction:-

The Opcode shown above determines the nature of the operation to be performed. The operands, Operand 1 and operand 2 identify the data on which operation has to be performed. The operand can be a memory location, a processor register, immediate value or logical data.

Now, as we have studied above, the instructions could be of many types. The operation specified in the instruction decides the nature of that instruction. Generalizing all types of instructions, they can be categorized into four types as follows:

- Instructions that transfers the data between the memory of the computer and processor register.

- Instructions that can perform arithmetic and logical operations on the data.

- Instructions controlling the sequencing of execution of instructions, like branch instruction.

- Instructions performing the I/O transfer i.e. transferring the data from internal storage to the external storage or device.

Register Transfer Notation

When it comes to ‘information transfer’ it requires a source location and a destination location. The source location is from where the value is to be read and the destination location is where the value is to be stored.

Here, the source or destination locations can be memory locations, processor registers or they can be the register in I/O subsystem. These locations are given a symbolic name for the convenience.

Below are the instructions for register transfer notations:

Instruction 1 R4 <- [VAR3]

Instruction 2 R4 <- [R3] + [R2]

The instruction 1 indicates the value in the memory location having symbolic name VAR3 is transferred to the processor register R4. Here, VAR 3 is placed in square bracket [ ], as the square bracket around a location denotes the content or value stored at that location.

The old content of R4 will get overwritten by the value of VAR3.

Similarly, in instruction 2 the value inside the processor register R3 and R2 is added and then stored in the processor register R4. Here, also the old content of R4 will get overwritten by the sum of R3 and R2.

These kinds of notations are called as Register Transfer Notation (RTN).

Always remember the value at the right-hand side of the RTN expression is value to be operated or considered for the transfer and the left-hand side is the name of the location where that value has to be stored.

The contents of operands mentioned at the RHS of RTN expression does not changes. But, the contents of the operand mention at LHS of RTN expression gets overwritten.

Assembly Language Notation

Assembly Language notations are used to represent the machine instructions. An assembly language instruction specifies the operation, that has to be performed and the operands that will be involved in the operation.

Assembly language instruction use mnemonics to denote the operations. These mnemonics are nothing but the abbreviation of the word that describes the nature of operation. Like, for addition it has Add, for Multiplication it has Mul, for division Div.

Let us overview the assembly language instruction.

Instruction 1 Load R4, VAR3

Instruction 2 Add R4, R3, R2

In instruction 1 the content in memory location VAR3 is loaded in processor register R4. After the execution of this instruction, the content of VAR3 will remain the same as before the execution of the instruction. But, the old content of R4 is overwritten by the content of VAR3.

In instruction 2 the content of the registers R3 and R2 are added and the sum is stored in register R4.

RISC and CISC Instruction set

Computers can be differentiated on the basis of the nature of their instruction set. There are two ways in which the instruction set for modern-day computer could be designed those are RISC and CISC.

Talking about Complex Instruction Set Computers (CISC), they were prevalent in the 1970s before the Reduced Instruction Set Computers (RISC) were introduced.

CSIC has complicated instruction sets which specifies more complicated operations. Some instructions in CISC would occupy more than one word in memory. Most of the modern-day CISC instruction has two address format.

Suppose we have to execute the below instruction in CISC instruction format.

C = A + B

In CISC format it would be as follow:

Move C, B

Add C, A

The content of memory location A and B will not get changed whereas, the content in C would be overwritten.

Move instruction has the general instruction format:

Move destination, source

Here, the source and destination could either be a memory location or a processor register.

The Move instruction has functionality similar to Load and Store instruction of RISC. But it has a difference too.

Like, in Load instruction source is a memory location and destination is a register. While in Store instruction source is a register and destination is a memory location.

But, in Move instruction both source and destination can either be a memory location or processor register or it can also be used to move immediate operands.

Now, Reduced Instruction Set Computers (RISC) has two important characteristics those are:

- Each instruction should in a single word in memory.

- It has Load/Store instruction to access memory operands.

In RISC instruction performing arithmetic and logic operation, all the operands must be in the processor register or either of one operand must be explicitly mentioned within the instruction. This is because RISC instruction can perform the arithmetic and logic operation only on the operand of processor registers.

At the time of program execution, all the instructions and data of the program must be present in computer memory. If some operands are expected to be in processor register before the operands can be operated, then it is done using Load instruction.

If we have to produce RISC instruction set for the following instruction:

C = A+ B

In RISC format the above instruction is:

Load R2, A

Load R3, B

Add R4, R3, R2 // three address format

Store R4, C

The general format for Load and Store:

Load destination, source //destination is processor register & source is a memory location

Store source, destination // destination is a memory location & source is a processor register

Instruction Sequencing and Execution

Execution of instruction is a two-step procedure. In the first step, the instruction is fetched from memory. In the second step, the instruction is executed.

First Step-> Instruction Fetch

The processor has a register named program counter which has the address of the instruction that has to be executed next. To start the execution of a program, the address of first instruction has to be placed in the program counter.

After the address of first instruction is placed in the program counter, the processor uses this address to fetch the first instruction. As soon as the first instruction is fetched the content in program counter is incremented by the word length (the group of n bits that can store a single, basic instruction) i.e. now, it has the address of next successive instruction to be executed.

After fetching the instruction from memory location it is placed in the instruction register of the processor.

Second Step -> Instruction execution

In the second step, the processor examines the instruction present in the instruction register and find out which operation has to be performed.

It first fetches the operands involved in the instruction from the memory or processor register. Then the processor performs the arithmetic and logical operation and stores the result in the destination location mention in the instruction.

During this time the content of program counter is incremented so that it could point next instruction for execution. This execution of instructions in increasing order of addresses is straight line sequencing.

Branching Instruction

Now, suppose we have to add n numbers. Their addresses in the symbolic form are Num1, Num2, Num3,…….NumN. So, the instructions for adding these n numbers are as follow:

Load R2, Num1

Load R3, Num2

Add R2, R3, R2

Load R3, Num3

Add R2, R3, R2

Load R3, Num4

Add R2, R3, R2

.

.

.

.

Load R3, NumN

Add R2, R3, R2

Store R2 SUM

Instead of writing this straight-line sequence of instruction we could implement a loop to this program. To add n numbers a loop has to be repeated n number of times.

Suppose there are n numbers to be added. So, this count value n is stored in the memory location N. Below is the instruction set specifying the loop to add n numbers

Load R2, N

Clear R3

Determine Next_number // Loop start

Load R5, Next_number

Add R3, R5

Sub R2, R2, #1

Branch if [R2]>0 Loop // Loop repeat

Store R3, SUM

In the above code “Branch if [R2]>0 Loop” is a branch instruction. This instruction loads the address of the next number in the program counter. The address of the next number to be added is a branch target.

The branch instruction we have used is the conditional branch instruction as it will perform loop until the value of R2 >0. As the condition R2>0 will become false it will stop performing the loop.

So this is all about the instruction format, sequencing and execution in computer architecture.

Leave a Reply