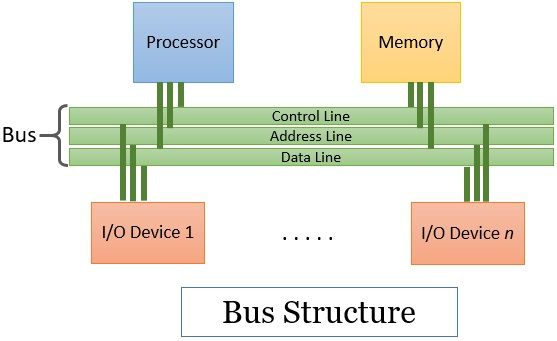

Bus structures in computer plays important role in connecting the internal components of the computer. The bus in the computer is the shared transmission medium. This means multiple components or devices use the same bus structure to transmit the information signals to each other.

At a time, only one pair of devices can use this bus to communicate with each other successfully. If multiple devices transmit the information signal over the bus at the same time, the signals overlap each other and get jumbled.

Bus Structure in Computer Architecture

A system bus has typically from fifty to hundreds of distinct lines where each line is meant for a certain function. These lines can be categorised into three functional groups i.e., data lines, address lines, and control lines. Let us discuss them one by one each.

1. Data Lines

Data lines coordinate in transferring the data among the system components. The data lines are collectively called data bus. A data bus may have 32 lines, 64 lines, 128 lines, or even more lines. The number of lines present in the data bus defines the width of the data bus.

Each data line is able to transfer only one bit at a time. So the number of data lines in a data bus determines how many bits it can transfer at a time. The performance of the system also depends on the width of the data bus.

2. Address Lines

The content of the address lines of the bus determines the source or destination of the data present on the data bus. The number of address lines together is referred to as the address bus. The number of address lines in the address bus determines its width.

The width of the address bus determines the memory capacity of the system. The content of address lines is also used for addressing I/O ports. The higher-order bits determine the bus module, and the lower-ordered bits determine the address of memory locations or I/O ports.

Whenever the processor has to read a word from memory, it simply places the address of the corresponding word on the address line.

3. Control Lines

The address lines and data lines are shared by all the components of the system, so there must be some means to control the use and access of data and address lines. The control signals placed on the control lines control the use and access to the address and data lines of the bus. The control signal consists of the command and timing information. Here the command in the control signal specifies the operation that has to be performed. And the timing information over the control signals specifies when the data and address information is valid.

The control lines include the lines for:

- Memory Write: This command causes the data on the data bus to be placed over the addressed memory location.

- Memory Read: This command causes the data on the addressed memory location to be placed on the data bus.

- I/O Write: The command over this control line causes the data on the data bus to be placed over the addressed I/O port.

- I/O Read: The command over this control line causes the data from the addressed I/O port to be placed over the data bus.

- Transfer ACK: This control line indicates the data has been received from the data bus or is placed over the data bus.

- Bus Request: This control line indicates that the component has requested control over the bus.

- Bus Grant: This control line indicates that the bus has been granted to the requesting component.

- Interrupt Request: This control line indicates that interrupts are pending.

- Interrupt ACK: This control line acknowledges when the pending interrupt is serviced.

- Clock: This control line is used to synchronize the operations.

- Reset: The bit information over this control line initializes all the modules.

Suppose a component connected to the bus wishes to send data to another connected component. In that case, it first has to acquire control over the bus, and then it can transfer the data to another component over the bus. The same happens when a component request data from another component.

During data transfer between two components, one component act as a master and the other act as a slave. The device initiating the data transfer is referred to as the master, and usually, it is a processor, or sometimes it may be some other device or component. The component addressed by the master component is referred to as a slave.

Timing in Bus

As we have seen, the bus’s control lines also provide timing information along with the command. Well, the way of deriving the timing information over the control line can be categorized in two ways:

1. Synchronous Bus

With the synchronous bus scheme, all the devices or components connected to the bus derive timing information over the control line referred to as the bus clock. Over the bus clock line, the clock transmits an alternating sequence of 1s and 0s at regular intervals. A single 1-0 transmission is considered a clock or bus cycle.

All the devices or components connected to the bus can read this bus clock line, and all the events start at the starting the clock cycle. Here the transmitting component and the receiving component are synchronized using the clock. The data is sent or received constantly and, therefore used for high-speed transmission.

2. Asynchronous Bus

The clock does not synchronise the transmitter and receiver components in this asynchronous bus scheme. Instead, the data transfer is controlled using a handshake protocol between the master component and the slave component.

Here, the component initiating the data transfer i.e. master component then gets ready for data transfer, and indicates this by activating its master-ready line and placing the address and command information over the bus.

Then all the connected component decodes the address on the address line to recognize which component is being addressed by the master component.

Now the addressed component performs the required operation and notifies the processor by activating its slave ready-line. Once the master recognizes the activated slave ready-line, it removes its control over the bus.

In this way, the occurrence of one event on the bus is followed by and depends on the occurrence of a previous event.

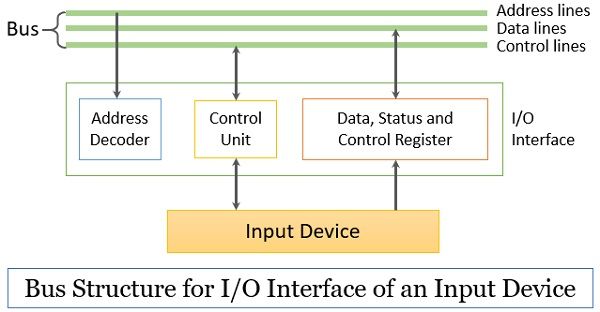

I/O Interface of Input Device Connected to Bus

In the section ahead, we will discuss how these three things over the bus are decoded by the I/O interface.

Each I/O device interface has a set of registers with unique addresses. Whenever the processor puts an address over the address line of the bus, it is examined by all the devices connected to the bus. Whichever device recognizes this address responds to the control operations issued on the control lines of the bus.

The processor issues read/write operation over the control lines of the bus, and the data corresponding to the read and write operation is transmitted over the data lines of the bus. Consider that we have an input device keyboard, and some data from the keyboard has to be issued to the processor; the machine instruction for the same is:

LOAD R2, DATAIN

Here the DATAIN is the data register of the Keyboard. This instruction reads the content from the DATAIN register of the keyboard and transfers the content to the R2 register of the processor. Similarly, the instruction below:

STORE R2, DATAOUT

Here consider that the DATAOUT register is the data register of a display device. So, this instruction will transfer the content of register R2 of the processor to the data register of the display device.

The control register and the status register of the I/O device interface have information relevant to the operation performed on or by the I/O device. The address decoder, control circuitry and the registers of the I/O interface coordinate in transferring the content to or from the I/O device.

So, this is all about the bus structure in computer architecture. We have seen how the bus plays a vital role in data transfer.

Anurag Raj says

That was a super helpful and detailed explanation there! I enjoyed it thoroughly. Didn’t struggle a bit to get what you meant to convey.

Thank You for the article. Helped a lot.

Hortensie V says

Love this article. Very helpfull. Thanks