Interrupt driven I/O is an approach to transfer data between ‘memory’ and ‘I/O devices’ through the ‘processor’. The other two techniques for the same are programmed I/O and direct memory access (DMA). The interrupt-driven I/O involves the use of interrupt to exchange data between I/O and memory.

In our previous content, programmed I/O we have seen it is a processor who keeps on checking whether the I/O module is ready for reception and transmission of data or whether the I/O module has completed the desired task or not. This long waiting of the processor deteriorates the performance of the system.

To improve the performance of the system an alternative approach can be used where after issuing the I/O command to the I/O module the processor can get itself busy doing some other work. In this way, the valuable time of the processor can be utilized.

Functioning of Interrupt Driven I/O

In this section, we will study how with the approach of interrupt-driven I/O the data is exchanged between memory and I/O through the processor. We will first see this entire scenario from the I/O module’s point of view and then from the processor’s point of view.

Consider that the data has to be stored in the main memory from the I/O module as input from the I/O module’s point of view.

1. For this, the processor issues a READ I/O command to the corresponding I/O module and proceeds with some other useful tasks. It does not wait for the I/O module to get ready with the desired data.

2. The I/O module then processes this READ I/O command and reads the data from the addressed peripheral device. The I/O module stores the read data into its data register and issues an interrupt signal to the processor over the control line in the system bus.

By sending the interrupted signal, the I/O module indicates the processor that now it is ready for transmitting the data. But, the I/O module has to wait until the processor asks for the data from the I/O module.

3. When the processor requests the data from the I/O, it places the data over the data line of the system bus. Once the I/O module transfers the data to the processor it set itself ready for another I/O transfer.

Now let us discuss this transfer of data between processor and I/O from the professor’s point of view.

1. So let’s again start, to retrieve data from the I/O module the processor issues a READ command and proceeds in doing something else.

For example, it starts executing some other program as it may be working on multiple programs at a time.

2. As we know that whenever the processor is executing any program, after every instruction cycle it checks for interrupts that have occurred. If it finds the pending interrupts it responds and serves the occurred interrupt.

3. The moment processor finds the interrupts by the I/O module, it suspends its current execution and saves the context (e.g., program counter, processor register) to serve the interrupt.

4. Now processor request data from the I/O module and accept the word of data over the data line. The processor stores this data onto the memory and restores the context of the program it was working on and resumes its execution.

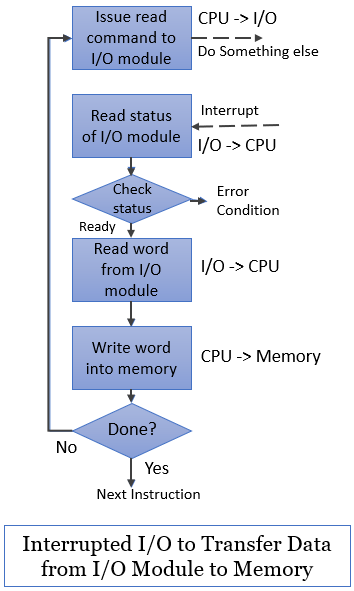

The figure below shows you how with the help of interrupt I/O the data transfer is carried out between memory and I/O. Though it is more efficient than programmed I/O still it wastes some of the processor’s time. As the transfer of data from memory to the I/O module or from the I/O module to memory passes through the processor.

Interrupt Servicing

Till now we have seen the transfer of data between the I/O and memory where the I/O module signals the processor by issuing an interrupt. Issuing an interrupt triggers many other events in processors hardware and software which we will discuss in detail in this section.

- The I/O device completes the task that the processor has issued to it through the I/O command and then it signals an interrupt to the processor.

- The processor executes its current instruction and then check for the interrupt.

- When the processor determines an interrupt it signals the corresponding I/O device with an acknowledgment that it has received an interrupt. Receiving the acknowledgment from the processor, the I/O device withdrwa its interrupt signal.

- The processor now has to transfer the control to the interrupt service routine. But before switching the control it has to save the information it requires to resume the execution of the program it was working on at the point of interrupt.

The least information that the processor will require to resume its work at the point of interrupt is the current status of the processor and the address of the next instruction to be executed. The processor saves its status in the register program status word (PSW) and the address of the next instruction to be executed in the program counter. The processor put this information onto the system control stack. - The processor loads the program counter with the address of the entry location of the appropriate interrupt service routine that will serve the occurred interrupt.

- Well depending on the computer architecture and the type of operating system you have there may be a single interrupt handling program for all types of interrupt or there may be a different program for each type of interrupt.

- In the case of several interrupt handling programs the processor has to determine which interrupt handling routine it has to invoke and this information is present in the interrupt signal issued to the processor by the I/O module. Once this information is acquired the processor starts the execution of the program service routine.

- The interrupt service routine serves the occurred interrupt for that the processor checks the status of the I/O device that signals the interrupt or the event that cause the interrupt. While serving the interrupt the processor may send some additional commands or acknowledge to the I/O device.

- When the interrupt is processed completely the processor restores its register values from the stack.

- Finally, the values of the program counter and program status word are restored from the stack and resume the execution of the interrupted program.

Note: A mechanism is implemented in the interface circuit of every device that controls whether the corresponding I/O device is allowed to signal an interrupt or not. This mechanism is implemented by enabling or disabling the interrupt-enable bit. This bit is present in the interface circuit of the device.

So, this is all about the interrupt-driven I/O. We have seen its advantage over the programmed I/O. Though there is more room for improvement i.e., there is still wastage of processor time as the entire data transfer includes the involvement of the processor.

DMA direct memory access is a solution to this problem as it lets the exchange of the data between the I/O device and memory without the involvement of the processor.

Arjun Poudel (from Nepal) says

Excellent explanation. Thanks so much!

Hamdan Zaheer says

This article is awesome. My teacher gave me an assignment from the unit she hasn’t taught us and I was really struggling with this topic. After reading many article and watching videos I found this article and this is the most detailed article on this topic. The thing that in this article, the process is explained from both the I/O module and processor’s point of view, really helped a lot.

Pierre says

Thank you! My book provided a terrible explanation of Memory Mapped I/O then immediately segwayed to Interrupt Driven I/O, I ended up think that Memory Mapped I/O was a method that achieves the same goals as Interrupt Driven IO, when it’s just how the devices are addressed.

Your explanation was so concise too, thank you.

Nithya says

This is a very nice article to learn about Interrupt driven I/O. It was very useful for my work. Thank you for sharing your knowledge.

Ajay says

Hello sir,

Your content is very informative. Keep growing.